システムの概要

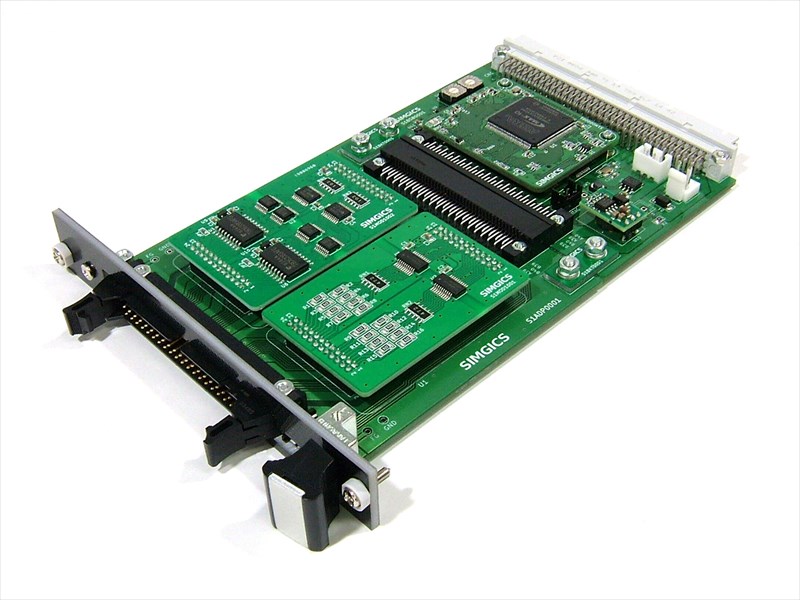

簡易的なデジタル入出力システムとして動作するシステムの例を示します。下記のハードウェア構成で動作する サンプルソフトウェア(FPGA HDL System Verilog, Python アプリケーション)を公開しますのでご利用ください。

- デジタル入力用FPGAファームウェア(S1FRM0001)

- デジタル出力用FPGAファームウェア(S1FRM0002)

- Raspberry Pi 用 Python アプリケーション

上記のFPGA ファームウェア、Python アプリケーションは、Apache License Version 2.0 ライセンスで公開します。この部分に関しては、改変して生成物を配布する場合でもソースコードの公開の義務はありません。

システムの特徴

- ボード間は、CANバスを通じて通信を行います。

ビットレート:1Mbps、最大バス長:40m(1Mbps時) - ステーションIDは、2~255 の範囲で設定できます。

- ステーション数は最大120まで追加できます。(CANドライバの上限)

- FPGAファームウェアは無償ライセンス版の開発ツールでプログラミング可能

Python アプリケーションの動作概要

| status_request.py | 各ステーションに対して状態の送信を要求する。 |

| message_monitor.py | CANメッセージのモニタを行う。(DIステーションから状態変化でメッセージが送出される。) |

| config_read.py | ベースボード上のFRAMに格納された先頭8バイトのデータを読む。 |

| config_write.py | ベースボード上のFRAMの先頭8バイトにデータを書き込む。デジタル入力では末尾の1バイトでチャタリングフィルターのディレー時間を設定する。 |

| do_cont.py | デジタル出力の制御信号を送信する。 |